Ivy Bridge Performance and Overclocking

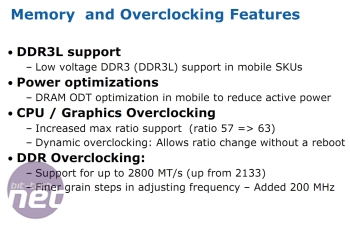

As we were just talking about the memory power optimisations of Ivy Bridge, albeit in mobile versions only, let’s kick off with performance enhancements to the memory controller. Ivy Bridge will officially support 1,600MHz DDR3 memory rather than 1,333MHz. As usual, though, motherboard manufacturers might add additional memory straps to allow even higher memory frequencies without needing to overclock the Base Clock.Speaking of which, there’s a new memory strap on offer: 200MHz. This should help fine-tune a memory overclock if you've tweaked the Base Clock- with 133MHz and 266MHz also on offer (and possibly 100MHz), you should be able nail a decent memory speed easily.

General overclocking remains the same on Ivy Bridge as it was on Sandy Bridge from what we can tell at this point. You’ll need to trick Turbo Boost by raising the power draw limit to a level at which it won’t interfere with your planned overclock.

Then you’re free to set as high a Turbo Boost limit as you can manage by applying the usual voltages to vcore, System Agent and so on. Tantalisingly, the maximum CPU multiplier for Ivy Bridge will be 63x rather than 57x, suggesting an even higher level of overclockability.

This wish is corroborated by Intel saying that the Ivy Bridge line-up ‘supports similar product offerings’ to the Sandy Bridge roster, but that the 22nm 3D transistors from which Ivy Bridge is made allow for higher performance per Watt. Add more Watts via more voltage, and you're likely to see a higher frequency than you would with a similar Sandy Bridge overclock.

Finally, it’ll be possible to overclock an Ivy Bridge CPU via its multiplier from within Windows in real time. This isn’t a great idea for an everyday overclock, though, as booting Windows should be seen as a necessary stress test for any overclock.

Performance Upgrades

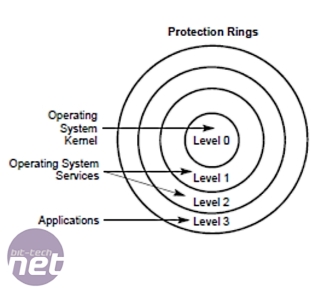

Intel has tweaked the execution cores and the ISA support of Ivy Bridge to increase its IPC (instructions per clock) performance, and there are also improvements in the performance of the Level 3 cache and the memory controller. As well as this, Intel has added a few new SSE instructions, while also adding some REP MOVSB/STOSB improvements to produce more consistent performance across string lengths. Joining these tweaks are four new instructions ‘for ring-3 access of Front Side and Graphics Side base registers.’ The ‘rings’ in question are security rings, with applications running in Ring-0 being the most privileged (pretty much only the operating system kernel) and so the most restricted from entering.

Joining these tweaks are four new instructions ‘for ring-3 access of Front Side and Graphics Side base registers.’ The ‘rings’ in question are security rings, with applications running in Ring-0 being the most privileged (pretty much only the operating system kernel) and so the most restricted from entering.User-run applications operate in Ring-3 and are ring-fenced from lower Rings, thus preventing malware from having sufficient privileges to kill the operating system or perform other nasty, low-level operations.

The improvements Intel has made to the Ring-3 base registers should also see some additional register-based performance if the software can take advantage of the new instructions. Specific security updates are discussed on page 6

Intel has also boosted the fp16 floating point format conversion instructions to enable ‘conversion between a 16-bit (compressed) floating point memory format and [a] 32-bit single-precision [format] (256-bit AVX and 128-bit SSE versions).’

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.